UNIVERSITY PARK, Pennsylvania — La legge di Moore, un principio fondamentale per la misurazione dei dispositivi elettronici, prevede che il numero di transistor su un chip raddoppierà ogni due anni, garantendo una maggiore potenza di calcolo, ma c'è un limite.

I chip più avanzati di oggi contengono circa 50 miliardi di transistor in un'area non più grande di una miniatura. Secondo i ricercatori della Penn State, il compito di stipare più transistor in quell’area ristretta sta diventando sempre più difficile.

In uno studio pubblicato oggi (10 gennaio) sulla rivista naturaSaptarshi Das, professore associato di scienze ingegneristiche e meccanica e coautore dello studio, e il suo team propongono una cura: implementare perfettamente l'integrazione 3D con materiali 2D.

Nel mondo dei semiconduttori, l'integrazione 3D significa impilare verticalmente più strati di dispositivi semiconduttori. Questo approccio non solo semplifica l'inserimento di più transistor a base di silicio su un chip di computer, comunemente denominato “più MOOR”, ma consente anche l'utilizzo di transistor realizzati con materiali 2D per integrare diverse funzioni all'interno di diversi strati dello stack. , un concetto noto come More than Moore.

Con il lavoro descritto nello studio, Saptarshi e il team dimostrano percorsi fattibili che vanno oltre l’ampliamento della tecnologia esistente per ottenere sia “Più-Più” che “Più-Più” attraverso l’integrazione 3D monolitica. L'integrazione monolitica 3D è un processo di produzione in cui i ricercatori fabbricano dispositivi direttamente sul dispositivo sottostante, rispetto al processo tradizionale di impilamento di strati prodotti in modo indipendente.

“L’integrazione monolitica 3D fornisce la più alta densità di connessioni verticali perché non si basa sulla connessione di due chip pre-modellati – che richiede piccole protuberanze in cui due chip sono uniti – in modo da avere più spazio per effettuare le connessioni”, ha affermato Najm Sakib. Assistente di ricerca laureato in scienze ingegneristiche e meccanica e coautore dello studio.

Secondo Darseth Jayachandran, ricercatore laureato in scienze ingegneristiche e meccaniche e coautore dello studio, l’integrazione 3D deve affrontare sfide significative, poiché i componenti convenzionali in silicio si scioglierebbero al di sotto delle temperature di lavorazione.

“Una sfida è il limite massimo della temperatura di processo di 450 gradi Celsius (C) per l'integrazione back-end di chip a base di silicio: il nostro approccio di integrazione filettata 3D riduce la temperatura significativamente al di sotto di 200 C”, ha affermato Jayachandran, spiegando che la temperatura operativa del tetto è la temperatura massima consentita prima di danneggiare le strutture prefabbricate. “I budget incompatibili per la temperatura di processo rendono difficile l’integrazione 3D monolitica con i wafer di silicio, ma i materiali 2D possono resistere alle temperature di processo necessarie”.

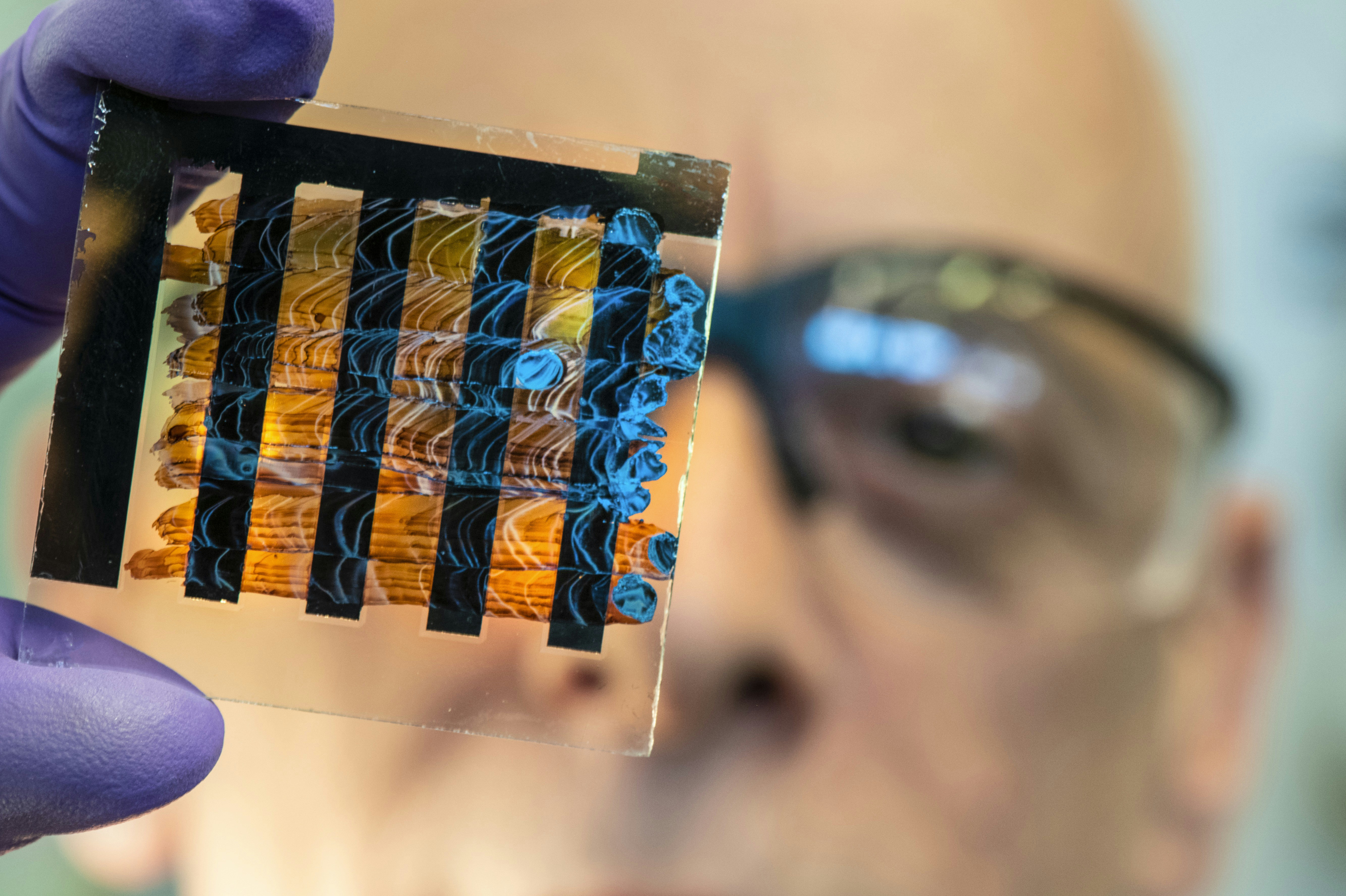

I ricercatori hanno utilizzato le tecnologie esistenti nel loro approccio, ma sono i primi a raggiungere con successo l’integrazione 3D monolitica su questa scala utilizzando transistor 2D costituiti da semiconduttori 2D chiamati dichalcogenuri di metalli di transizione.

La capacità di impilare verticalmente i dispositivi in un’integrazione 3D ha consentito anche un’elaborazione più efficiente dal punto di vista energetico perché ha risolto un problema sorprendente per cose piccole come i transistor su un chip di computer: la distanza.

“Impilando i dispositivi verticalmente uno sopra l'altro, si riduce la distanza tra loro e quindi si riducono il ritardo e il consumo energetico”, ha affermato Rahul Pendurthi, assistente di ricerca laureato in scienze ingegneristiche, meccaniche e di collaborazione presso l'Università di Harvard. -Autore corrispondente dello studio.

Riducendo la distanza tra i dispositivi, i ricercatori hanno ottenuto “più Moore”. Incorporando transistor realizzati con materiali 2D, i ricercatori hanno soddisfatto anche il criterio More-than-More. I materiali 2D sono noti per le loro proprietà elettroniche e ottiche uniche, inclusa la sensibilità alla luce, che li rendono ideali come sensori. Ciò è utile, hanno detto i ricercatori, poiché il numero di dispositivi e periferiche connessi – cose come smartphone o stazioni meteorologiche domestiche wireless che raccolgono dati “ai margini” della rete – continua ad aumentare.

“'More Than More' si riferisce a un concetto nel mondo della tecnologia in cui non solo stiamo realizzando chip per computer più piccoli e più veloci, ma anche con più funzionalità”, ha affermato Moatasem Al-Karim Sadaf, un assistente di ricerca laureato in ingegneria e scienze meccaniche e co-investigatore. Autore dello studio. “Si tratta di aggiungere nuove e utili funzionalità ai nostri dispositivi elettronici, come sensori migliori, una migliore gestione della batteria o altre funzioni speciali, per rendere i nostri gadget più intelligenti e versatili.”

L'uso di dispositivi 2D per l'integrazione 3D presenta numerosi altri vantaggi, hanno affermato i ricercatori. Uno è la mobilità dei superconduttori, che si riferisce al modo in cui la carica elettrica viene trasportata nei materiali semiconduttori. L'altro motivo è che è estremamente sottile, consentendo ai ricercatori di inserire più transistor a ciascun livello di integrazione 3D e consentendo una maggiore potenza di calcolo.

Mentre la maggior parte della ricerca accademica coinvolge prototipi su piccola scala, questo studio ha dimostrato l’integrazione 3D su larga scala, caratterizzando decine di migliaia di dispositivi. Secondo Das, questo risultato colma il divario tra il mondo accademico e l'industria e potrebbe portare a future partnership poiché l'industria sfrutta le competenze e le strutture dei materiali 2D di Penn State. I progressi nella misurazione sono stati resi possibili dalla disponibilità di dichalcogenuri di metalli di transizione su scala wafer di alta qualità sviluppati dai ricercatori del 2D Crystal Consortium (2DCC-MIP) presso Penn State, la piattaforma di innovazione dei materiali della National Science Foundation (NSF) degli Stati Uniti. e gli Istituti nazionali di tecnologia. Facilità dell'utente.

“Questa svolta dimostra ancora una volta il ruolo essenziale della ricerca sui materiali come fondamento per l’industria dei semiconduttori e la competitività degli Stati Uniti”, ha affermato Charles Ying, direttore del NSF Materials Innovation Platforms Program. “Anni di sforzi da parte del 2D Crystal Consortium della Penn State per migliorare la qualità e le dimensioni dei materiali 2D hanno reso possibile ottenere l’integrazione dei semiconduttori 3D a una dimensione che potrebbe essere trasformativa per l’elettronica”.

Secondo Das questo progresso tecnologico è solo il primo passo.

“La nostra capacità di dimostrare un gran numero di dispositivi, su scala wafer, dimostra che siamo stati in grado di tradurre questa ricerca su una scala che può essere apprezzata dall'industria dei semiconduttori”, ha affermato Das. “Abbiamo inserito 30.000 transistor in ogni strato, il che sarebbe un record. Ciò pone Penn State in una posizione davvero unica per guidare parte del lavoro e collaborare con l'industria dei semiconduttori statunitense nel portare avanti questa ricerca.”

Oltre a Das, Jayachandran, Pendurthi, Sadaf e Saqib, altri autori includono Andrew Pannone, uno studente di dottorato in ingegneria e scienze meccaniche; Chen Chen, assistente ricercatore presso 2DCC-MIP; Weiying Han, ricercatore post-dottorato in ingegneria meccanica; Nicholas Trainor, dottorando in Scienza e Ingegneria dei Materiali; Shalini Kumari, ricercatrice post-dottorato; Thomas McKnight, dottorando in scienza e ingegneria dei materiali; Joan Redwing, Direttore del 2DCC-MIP e Professore emerito di Scienza e Ingegneria dei Materiali e di Ingegneria Elettrica; Yang Yang, assistente professore di ingegneria e scienze meccaniche.

La National Science Foundation degli Stati Uniti e l'Esercito Research Office hanno sostenuto questa ricerca.

/Liberazione generale. Questo materiale dell'organizzazione/degli autori originali può essere di natura cronologica ed è modificato per motivi di chiarezza, stile e lunghezza. Mirage.News non assume posizioni aziendali o partiti e tutte le opinioni, posizioni e conclusioni qui espresse sono esclusivamente quelle dell'autore(i). Visualizza integralmente qui.

“Internet savvy. TV fan. Infuriatingly humble analyst. Unapologetic Twitter pioneer. Freelance coffee fanatic.”